次世代半導体製造向けの極微細穴あけ加工を実現

業種横断の協働拠点で先端半導体をけん引.

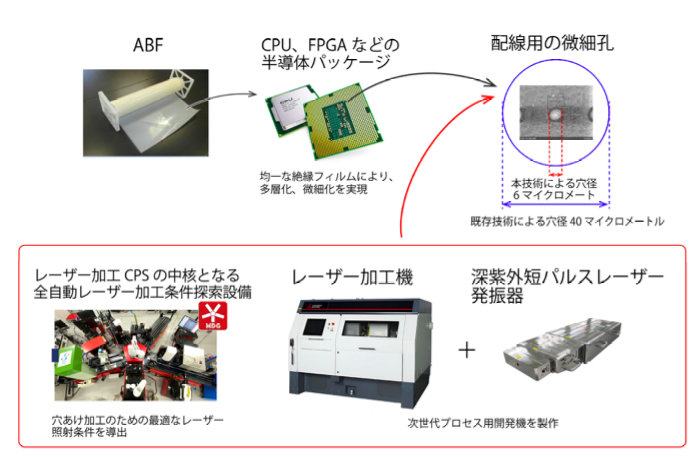

図1:本成果の概要。(上段)CPUなどの半導体のパッケージングで広く用いられている味の素ファインテク ノのABFに、次世代のニーズに対応する、10マイクロメートル以下の微細穴あけを実現。(下段)スペクトロ ニクスが開発した深紫外短パルスレーザーを、三菱電機が次世代レーザープロセス用の開発機に組み込 み、東京大学のレーザー加工プロセスのCPS化技術を活用して、開発

1. 発表者:

- 小林 洋平 : (東京大学物性研究所 教授)

- 真子 玄迅 : (味の素ファインテクノ株式会社 取締役執行役員 電子材料事業部長)

- 長岡 弘太朗 : (三菱電機株式会社 先端技術総合研究所 駆動制御システム技術部長)

- 岡田 穣治 : (スペクトロニクス株式会社 取締役)

2. 発表のポイント:

- 次世代の半導体製造に資する10マイクロメートル以下を満たす、6マイクロメートル以下の穴あけを 高品質かつ高生産性を維持し実現できることを実証

- 東京大学を産学官協創の拠点として、各法人が強みを持つ半導体に関連する最新の基盤技術を 集結し開発

- 半導体パッケージ基板のさらなる微細化や高品位化を目指すことで、次世代半導体産業における 日本の競争力強化に貢献

3. 概要

国立大学法人東京大学(総長 藤井 輝夫 以下、東京大学)、味の素ファインテクノ株式会社(代表取 締役社長 岡安 寿明 以下、味の素ファインテクノ)、三菱電機株式会社(代表執行役 執行役社長 漆間 啓 以下、三菱電機)、スペクトロニクス株式会社(代表取締役社長 長岡 由木彦 以下、スペクトロニクス) はこのたび、次世代の半導体製造工程に必要な、パッケージ基板への6マイクロメートル以下という極微細 レーザー穴あけ加工技術を開発しました。現在用いられている回路基板の穴径は約40マイクロメートルで す。次世代半導体製造のためには、穴径が10マイクロメートル以下であることが求められていますが、実 際の製造に堪える技術の形で実現が課題となっていました。

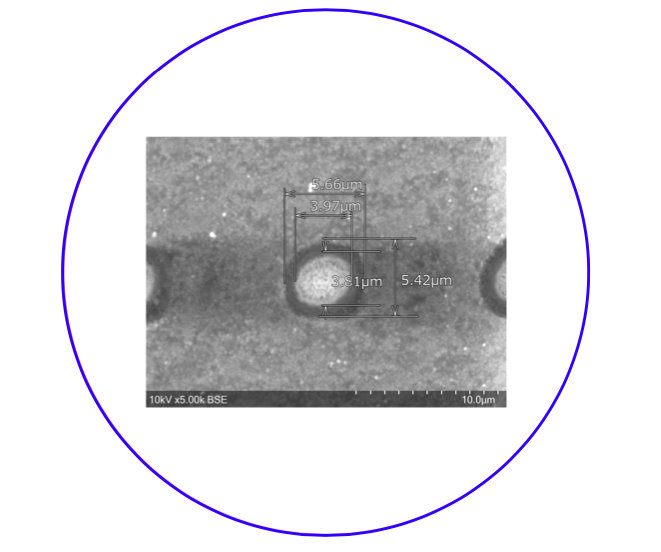

図2:ABFに高速スキャンで6マイクロメートルの穴をあけたものを電子顕微鏡写真で撮影。穴の内側で白く 見えるのは底面の銅薄膜。黒く見えるのが穴の側面。写真を囲む青丸は既存技術で用いられている40マ イクロメートル穴に相当するサイズ

今回、東京大学が運用している「TACMIコンソーシアム(注1)」において、半導体製造に関する異なる強 みを持つ法人が業種を超えて連携・開発したことにより、次世代の半導体製造工程に資する技術を開発し ました。本技術は半導体のさらなる微細化や複雑化するチップレット技術(注2)を支え、消費電力の削減や ポスト5G、電気自動車(EV)対応などへつながることが期待されます。

4法人は今後も連携して、半導体パッケージ基板のさらなる微細化や高品位化を目指し、次世代半導体 産業における日本の競争力強化に貢献してまいります。

本成果の技術に関する詳細は、2022年10月26日から台湾・台北で開催される国際会議IMPACT2022で 報告されます。

4.背景

半導体は、パソコンのみならず生活のあらゆる場面でICTのインフラを支える基盤となっており、社会の デジタル化が進むにつれて、生活のあらゆる場面で必要になっています。その半導体のさらなる微細化、 高性能化によって、より豊かな生活・便利な生活が現実のものとなっていきます。特に、昨今の急速な電気 自動車(EV)や自動運転技術の開発の進展により、これからますます高度な半導体が生活の中で活用さ れていくと予測されています。

現在、CPUに代表される高度な半導体においては、パッケージ基板のビルドアップ材料(注3)として味の 素ビルドアップフィルム®(ABF、注4)が広く用いられており、ABFに対してレーザーを用いて多数の微細な 穴あけ加工をして、銅めっきすることによって電気的な微細配線をしています。現在用いられている穴径は 40マイクロメートル程度であり、加工に用いるレーザーの波長が長いために、これ以上の微細穴あけは困 難でした。極端紫外光(EUV:Extreme Ultra-violet)リソグラフィ技術(注5)の進展により、半導体の微細化 や半導体構造のチップレット化など半導体を取り巻く環境が大きく変化する現在、ABFの微細穴あけに要 求される穴径はより一層の微細化が求められています。

ABF を製造・販売する味の素ファインテクノ、レーザー加工機を開発する三菱電機、新たな深紫外短パ ルスレーザーを製造・販売するスペクトロニクス、レーザー加工プロセスのサイバーフィジカルシステム (CPS:Cyber-Physical System、注6)化による知的生産技術研究を内閣府戦略的創造イノベーションプロ グラム(SIP:Strategic Innovation Program)において推進する東京大学は、レーザー加工のスマート化を目 指す産学官協創拠点「TACMI コンソーシアム(運営:東京大学)」にそれぞれの強みとなる技術を持ち寄り、 次世代の半導体製造工程に資する技術開発・評価に取り組んできました。

5.発表内容

今回、4法人の連携で目指したのは、次世代半導体製造に資する10マイクロメートル以下の穴径の微細 穴を、製造のニーズを満たす品質で、製造ラインの生産能力も視野に入れて実現することです(図1)。銅 薄膜上に厚さ5マイクロメートルのABFを配置して、これにレーザー微細穴あけ加工を実施しました。レーザ ーにはスペクトロニクスが開発・販売している波長266ナノメートルでピコ秒のパルス幅の深紫外レーザーを 用い、レーザー加工機には三菱電機が深紫外短パルスレーザーを特別に組み込んだ、次世代プロセス用 開発機を用いました。

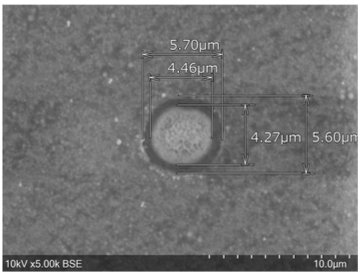

東京大学がSIP事業で開発する、加工プロセスを最適化するCPS型レーザー加工機 システムの成果も取り入れた結果、6マイクロメートル以下の極微細穴あけ加工を実現しました(図2)。実 現した微細穴は穴径が6マイクロメートル以下であるとともに、加工能力については、1秒当たり数千穴を実 現しています。また、高品位加工用のパラメータを用いることで、6マイクロメートルの直径において、上面 の穴径と下面の穴径の比として定義されるテーパー度は品質基準値の75%に達することがわかりました (図3)。これらは、次世代の半導体製造におけるパッケージ基板に対する基本的な要求に応えたものとな っています。

図3:ABFに微細かつ高品位穴あけを目指した例。テーパー度は75%。穴の側面が小さいことがわかる

本研究開発は、レーザー加工のスマート化を目指す産学官協創の拠点として東京大学が運用する 「TACMIコンソーシアム」において、各法人が強みを持つ半導体に関連する最新の基盤技術を集結して実 証を進めています。TACMIコンソーシアムでは、加工条件の探索が非常に困難であるレーザー加工分野に おいて、さまざまな加工ニーズや仕様に合わせた条件を迅速に見つけ出すスマート化技術に取り組んでい ます。本技術は、微細化・複雑化が進む次世代半導体製造において、チップレット技術、マルチスケールデ バイス化などを支える後工程に必要とされている技術であり、電気自動車(EV)の開発などでますます高度 化の需要が高まる先端半導体製造での活用が期待されています。

6.今後の展開

4法人は今後も連携して、さまざまな加工ニーズや仕様に合わせたレーザー加工のプロセス条件を迅 速に見つけ出すスマート化技術の開発と実証に取り組み、個別需要に合わせたカスタマイズを加速するこ とで、半導体製造ファブなどのユーザー企業への展開を進め、次世代の半導体産業における日本の競争 力強化に貢献していきます。また、TACMIコンソーシアムでは、今後も様々なモノづくりニーズに応えていくために、業種や分野を横 断する産学協創活動を推進していきます。

7.用語解説

- (注1)TACMIコンソーシアム: 東京大学により産学官連携で光ものづくり協創を推進するため2017年10月30日に設立。高効率レーザ ープロセッシング推進コンソーシアム(Consortium for Technological Approaches toward Cool laser Manufacturing with Intelligence)より、TACMI コンソーシアム。公式サイト http://www.utripl.u-tokyo.ac.jp/tacmi/. 国費プロジェクト等で開発した最先端のレーザー光源および加工機を集約したレーザー加工プラットフォ ームを有しています。上市前の設備を困難な加工ニーズを持つユーザー企業に開放することでシーズとニ ーズを実践的にマッチングさせ、未来を方向付ける場としての役割を果たしています。

- (注2)チップレット化(チップレット技術): 従来は1つのチップ上にプロセッサーやメモリーといったロジック構成要素を一体で製造していましたが、これを構成要素ごとに別チップとして製造した上で、パッケージ基板上に組み合わせて実装することで、一 体のパッケージとして動作するよう製造する技術およびその手法。

- (注3)ビルドアップ材料: 絶縁層と導体層を交互に形成して多層の基板を製造するビルドアップ工法に用いられる材料。厚みの均 一性や作業性などが優れている点からフィルム形態の材料が広く使用されています。レーザー加工により ビアを形成した後、銅めっきで回路形成する方法が一般的。

- (注4)ABF (Ajinomoto Build-up Film ®): PC の心臓部である高性能半導体(CPU)には「味の素ビルドアップフィルム® (ABF)」という層間絶縁材が使われており、現在では全世界の主要なパソコンのほぼ 100%のシェアに達しています。

- (注5)リソグラフィ技術: 露光装置を用いて、フォトマスクに描画された半導体の回路パターンをシリコンウェハ上のレジストに転 写する技術。

- (注6)サイバーフィジカルシステム(CPS:Cyber-Physical system) サイバー空間(仮想空間)とフィジカル空間(現実空間)を高度に融合させたシステム。経済発展と社 的課題の解決を両立し、一人一人の人間が中心となる社会であるSociety 5.0 実現のためには、CPSを活 用して社会の全体最適化を効率良く進めることが鍵とされています。