www.engineering-japan.com

04

'22

Written on Modified on

超小型SOD-962パッケージ採用により機器への高密度実装に貢献する過電圧保護用ツェナーダイオード

当社は、開閉サージや誘導雷サージ[注1]、静電気放電 (ESD)[注2]から半導体デバイスを保護するツェナーダイオード「CSLZシリーズ」を製品化しました。標準ツェナー電圧5.6 Vから30 Vの範囲で10品種のラインアップになります。

新製品は、ナノ秒オーダーのESD[注2]やマイクロ秒からミリ秒オーダーの開閉サージ、直流に近い過電圧から半導体デバイスを保護します。

パッケージは、標準実装面積0.1984 mm2の超小型SOD-962[注3]を当社ツェナーダイオードに初めて採用することで、SOD-523[注4]の当社既存製品[注5]と比べて、実装面積を約85 %削減しました。これにより、機器への高密度実装に対応します。

基板の有効活用と、機器の信頼性向上に貢献します。

- [注1] @IEC61000-4-5、tp=8/20 μs

- [注2] @IEC61000-4-2

- [注3] 当社パッケージ名称 : SL2

- [注4] 当社パッケージ名称 : ESC

- [注5] CEZシリーズ

応用機器

電子機器 (IoT機器、モバイル機器など)

新製品の主な特長

- 高密度実装に適したSOD-962[注3]パッケージ : 0.62 mm × 0.32 mm × 0.3 mm (typ.)

- マイクロ秒からミリ秒オーダーの長いパルス幅のサージ保護が可能

- 幅広いツェナー電圧ラインアップ : VZ (typ.)=5.6 V~30 V

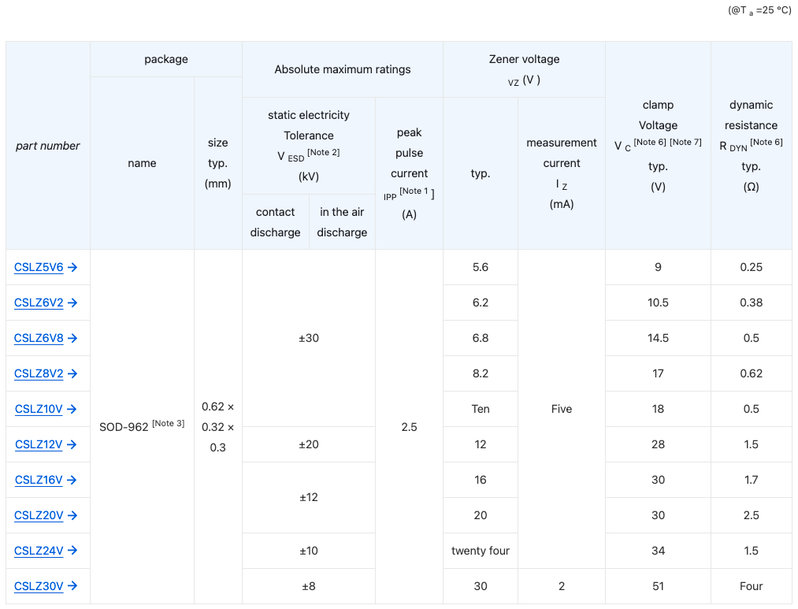

新製品の主な仕様

- [注6] TLPパラメーター : Z0=50 Ω、tp=100 ns、tr=300 ps、averaging window : t1=30 ns~t2=60 ns、ダイナミック抵抗はTLP特性のITLP1=8 A~ITLP2=16 A間で最小2乗法を用いて抽出しています。

- [注7] ITLP=8 A

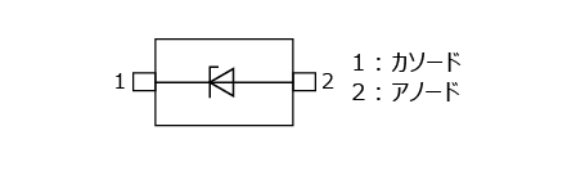

端子配置図

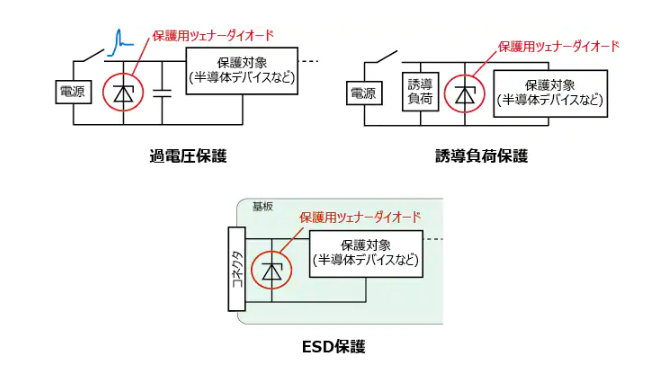

応用回路例

注 : この応⽤回路例は参考例であり、量産設計に際しては⼗分な評価を⾏ってください。また、⼯業所有権の使⽤の許諾を⾏うものではありません。

www.toshiba.com